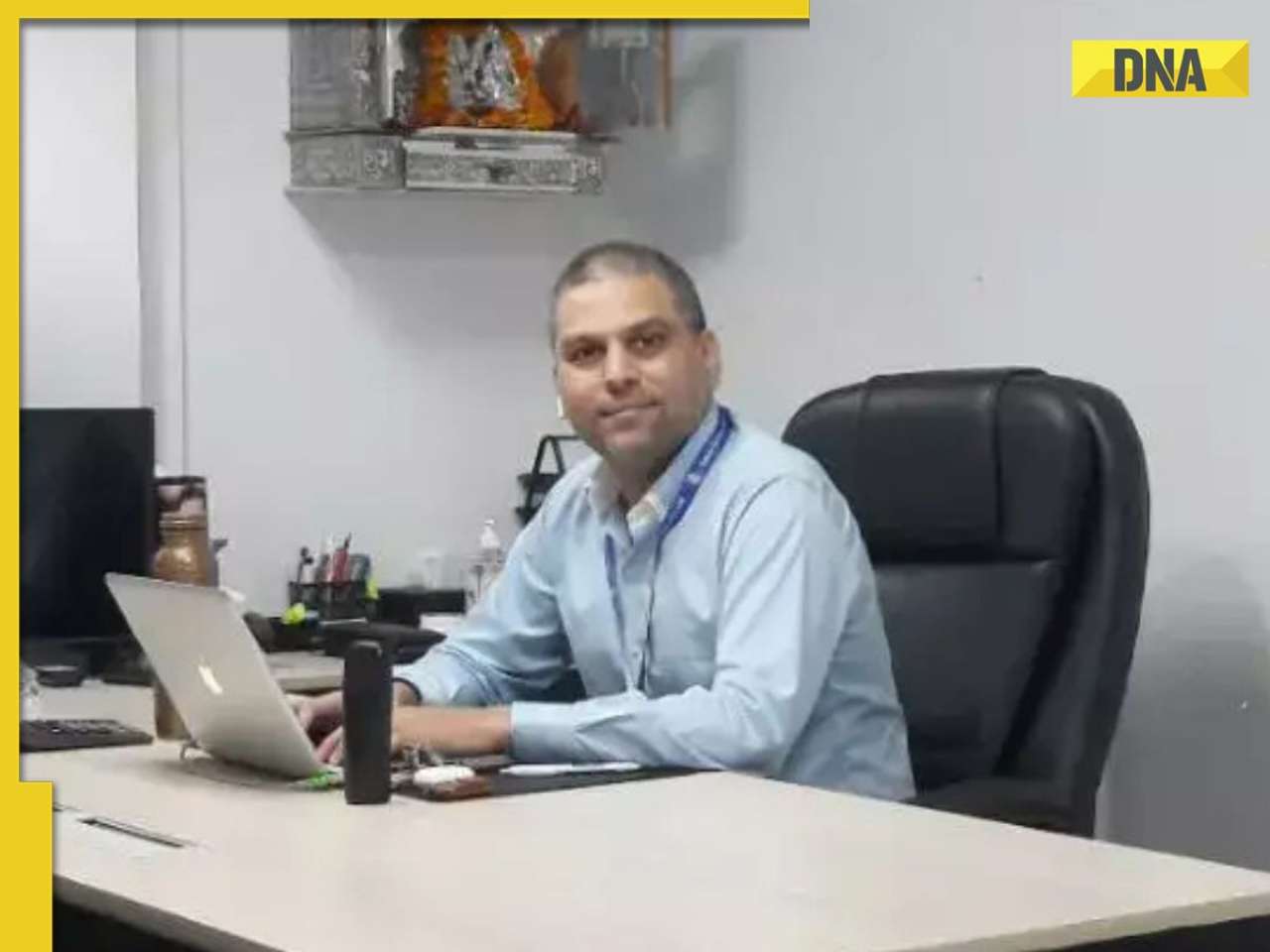

Sri Harsha Grandhi, a semiconductor engineer, advances high-speed memory systems and IO circuits, integrating AI and diverse technologies to build intelligent hardware.

Sri Harsha Grandhi is determined to increase what is achieved in the world of semiconductor engineering a world where things are complex as dealing with billions of transistors and where every nanosecond can spell the difference between success and failure. Working at NBC in a high-power position (Mixed-Signal and Analog Design Engineer) of over eight years, he has contributed significantly towards the advancement of enthusiastic memory systems architecture.

He is heavily engaged in 3D NAND memory works, and his work covered the entire design cycle including pre-silicon and post-silicon implementation. His inventions have been influential in development of high-speed datapaths and IO circuits which, in addition to their impressive performance measure, are also characterized by long-term reliability. His broad base in VLSI design, embedded systems and signal processing yields both technical breadth and multi-disciplinary flexibility to this emerging and rapidly changing environment.

His E.D.A. tasks are to develop and fine tune entire datapath systems every day and to make sure timing, power, and leakage all pass extremely high qualifications. He uses RTL vector development, SVA assertions, XA simulations to verify timing margins that can make stable and high speed operations across deep memory hierarchy.

One of the most critically discussed and cutomized topics is that of Leading Edge Circuit Design Across IO Speeds and Silicon Lifecycles.

Besides being involved in datapath design, he has been busy in the design of high-speed serializer and transmitter circuit designs, spanning IO rates of 1.2GT/s to 4GT/s. They include built in Duty cycle correction and advance clock distribution networks, so that they will give consistent and predictable behaviour under varying processes, aging and far-corner conditions.

An important technical contribution to his work has been development of an optimization approach to validation of ONFI AC specifications. This novel solution has significantly increased the accuracy of simulation and better match of it with a real-silicon behavior so that the performance characteristics would not vary depending on the stress and operating environments in the real world.

In several successful tape-outs, he has directed layout implementation, set strong power/signal distribution architectures and maintained IR drop constraints and LT reliability requirements. During post-silicon activity he collaborates with the validation and product teams to troubleshoot performance issues, perform root-cause analysis and inform architectural improvements in subsequent design versions.

In the context of simulation-to-silicon correlation in high-speed datapath IO configurations he has authored scalable multi-phase and multi-ratio serializer architectures, and automation frameworks that dramatically reduce the steps required to validate, verify, and analyse datapath performances.

During the pre-tapeout process, he owns AC/DC simulations, produces IBIS models and performs thorough reliability testing. His efficient participation in circuit design, system integration, layout coordination and post-layout debugging activities helps to deliver silicon that performs and delivers well against design objectives, in a timely and cost-effective manner to help deliver quality silicon on time and in volumes.

Tomorrow engineering: Convergence, Intelligence and Mentorship

Having more than 42 peer-reviewed articles he has published his works in a broad area of knowledge which includes VLSI, embedded systems, wireless communication, 5G/6G networks, IoT, Internet of Vehicles (IoV), UAV technologies, and power electronics. This wide range is determined by his commitment to connect circuit-level novelty and technology ecosystems at scale.

His other achievements also include the design of ZQ calibration system and NBTI aging protection circuitry, both were critical to silicon reliability spanning extended operating lifetimes. He is also an expert at verifying high speed IOs under Monte Carlo and PVT (process, voltage, temperature) corners to meet high robustness of performance requirements throughout the product lifecycle.

He comprehends the dilemma of speed, power and the area.

It is not a numbers game, says Grandhi. It is not only about knowledge in how circuits perform in time, under pressure, and its variability.

To respond to that challenge, he has developed scalable automation tools that would be adjustable to the changes in simulation environments and PDKs. His architecture techniques mediate system-level requirements of performance with the requirements of feasibility at the circuit level, as systems increasingly need integration and IO rates to keep pace.

In the future, he envisages an immense possibilities of a convergence of domains. The future is in the integration of VLSI, embedded platforms and wireless communication into coherent, intelligent hardware able to support edge computing, autonomous navigation and always connected systems.

Specifically, he views with great enthusiasm the way in which AI and machine learning are transforming engineering processes.

He thinks it has only begun with semantic analysis of the flow of AI-enhanced simulations and verification. They will drastically transform the way we work at the level of the transistor faster, smarter and more confidently.

Moreover, his effort is intensively overlapping with the new fields that are changing the ways in which the hardware is designed and implemented:

In circuit validation powered by AI/ML, he merges the deep learning models such as Convolutional Neural Networks (CNNs) and Long-Short Term Memory (LSTM) to make the validation predictions of any anomalies and automate the validation process. The models have made it possible to perform simulation with more accuracy and the design cycle reduction and accuracy in timing-sensitive datapaths.

Work In the area of IoT-systems in health care, industrial automation, and smart transport, his work is in the design of silicon-level architectures with an emphasis on low-power, real-time responsiveness and resilience to environmental variation. Such designs are the necessity of edge computing and sensor-combined architecture where neither speed nor trustworthiness are optional.

In robotics and automation, particularly cloud-connected manufacturing and rehabilitative solutions, he donates datapath and IO technology that is used to realize fine actuation and real-time data manipulation. His equipment is designed to work with dynamic workload that such applications require.

In signal processing he uses methodologies like wavelet and event detection algorithms in the real-time implemented on micro controllers to develop intelligent embedded systems. The resource efficient systems have been optimized and used in the monitoring, diagnostics, and controls.

His IO architectures allow highly fast data transfer and network synchronization to support the 5G/6G wireless systems to cover the requirements of the smart cities, autonomous vehicles, and edge-connected devices.

Such inputs do not only add the technical strength of his work but also demonstrate a greater dedication to creating systems which break theory and practice in various dynamic industries.

In addition to engineering, he expresses his enthusiasm over mentorship and pedagogy.

According to Grandhi, innovation is not performed out of a vacuum. It is all about giving, passing on the wisdom and knowledge, instilling the appetite to know and discover and helping people face those difficult challenges with a sense of purpose and integrity.

The name of Sri Harsha Grandhi About

Sri Harsha Grandhi is a Mixed-Signal, Analog Design Engineer, having a more than seven year experience in the Semiconductor Industry. His fields of interests are high-speed datapath architecture, multi-speed IO systems and simulation-to-silicon correlation. Having 45+ peer-reviewed papers in the areas of VLSI, embedded systems, and wireless communication, he is engaged in the development of intelligent, reliable, and adaptive hardware technologies.

'Amitabh Bachchan was sitting jobless at home after 11 flops...': Javed Akhtar reminisces about pitching Zanjeer to Big B, says 'Jaya Bachchan never...'

'Amitabh Bachchan was sitting jobless at home after 11 flops...': Javed Akhtar reminisces about pitching Zanjeer to Big B, says 'Jaya Bachchan never...' Good news for Railway passengers! Indian Railways rolls out new ticket booking rules for...

Good news for Railway passengers! Indian Railways rolls out new ticket booking rules for... BIG Update on Noida's Jewar International Airport Expansion: 4600 families, 7 schools affected as government to acquire...

BIG Update on Noida's Jewar International Airport Expansion: 4600 families, 7 schools affected as government to acquire... 'It was like indulging a little child': Producer Suneel Darshan says working with Sunny Deol was 'darkest chapter' of his life and career because...

'It was like indulging a little child': Producer Suneel Darshan says working with Sunny Deol was 'darkest chapter' of his life and career because... India issues advisory for Indians in Cambodia amid clash with Thailand

India issues advisory for Indians in Cambodia amid clash with Thailand Other than heart attacks or BP : 7 hidden heart conditions triggered by oily foods

Other than heart attacks or BP : 7 hidden heart conditions triggered by oily foods 7 most captivating space images captured by NASA you need to see

7 most captivating space images captured by NASA you need to see AI-remagined famous Bollywood father-son duos will leave you in splits

AI-remagined famous Bollywood father-son duos will leave you in splits 7 superfoods that boost hair growth naturally

7 superfoods that boost hair growth naturally Confused between Forex and Credit cards for your international trip? Learn which saves more

Confused between Forex and Credit cards for your international trip? Learn which saves more Tata Harrier EV Review | Most Advanced Electric SUV from Tata?

Tata Harrier EV Review | Most Advanced Electric SUV from Tata? Vida VX2 Plus Electric Scooter Review: Range, Power & Real-World Ride Tested!

Vida VX2 Plus Electric Scooter Review: Range, Power & Real-World Ride Tested! MG M9 Electric Review | Luxury EV with Jet-Style Rear Seats! Pros & Cons

MG M9 Electric Review | Luxury EV with Jet-Style Rear Seats! Pros & Cons Iphone Fold: Apple’s iPhone Fold Could Solve Samsung’s Biggest Foldable Problem | Samsung Z Fold 7

Iphone Fold: Apple’s iPhone Fold Could Solve Samsung’s Biggest Foldable Problem | Samsung Z Fold 7 Trump News: Congress Seeks Answers On Trump's Alleged Mediation In Operation Sindoor

Trump News: Congress Seeks Answers On Trump's Alleged Mediation In Operation Sindoor This man becomes world's highest-earning billionaire in 2025, beats Elon Musk and Jeff Bezos, Mukesh Ambani is at...

This man becomes world's highest-earning billionaire in 2025, beats Elon Musk and Jeff Bezos, Mukesh Ambani is at... Meet man who built Rs 200,000,000 empire after two failed ventures, his business is..., net worth is Rs...

Meet man who built Rs 200,000,000 empire after two failed ventures, his business is..., net worth is Rs... Meet man, founder of app under govt lens, also owns Rs 1000000000 business, he is..., his educational qualification is...

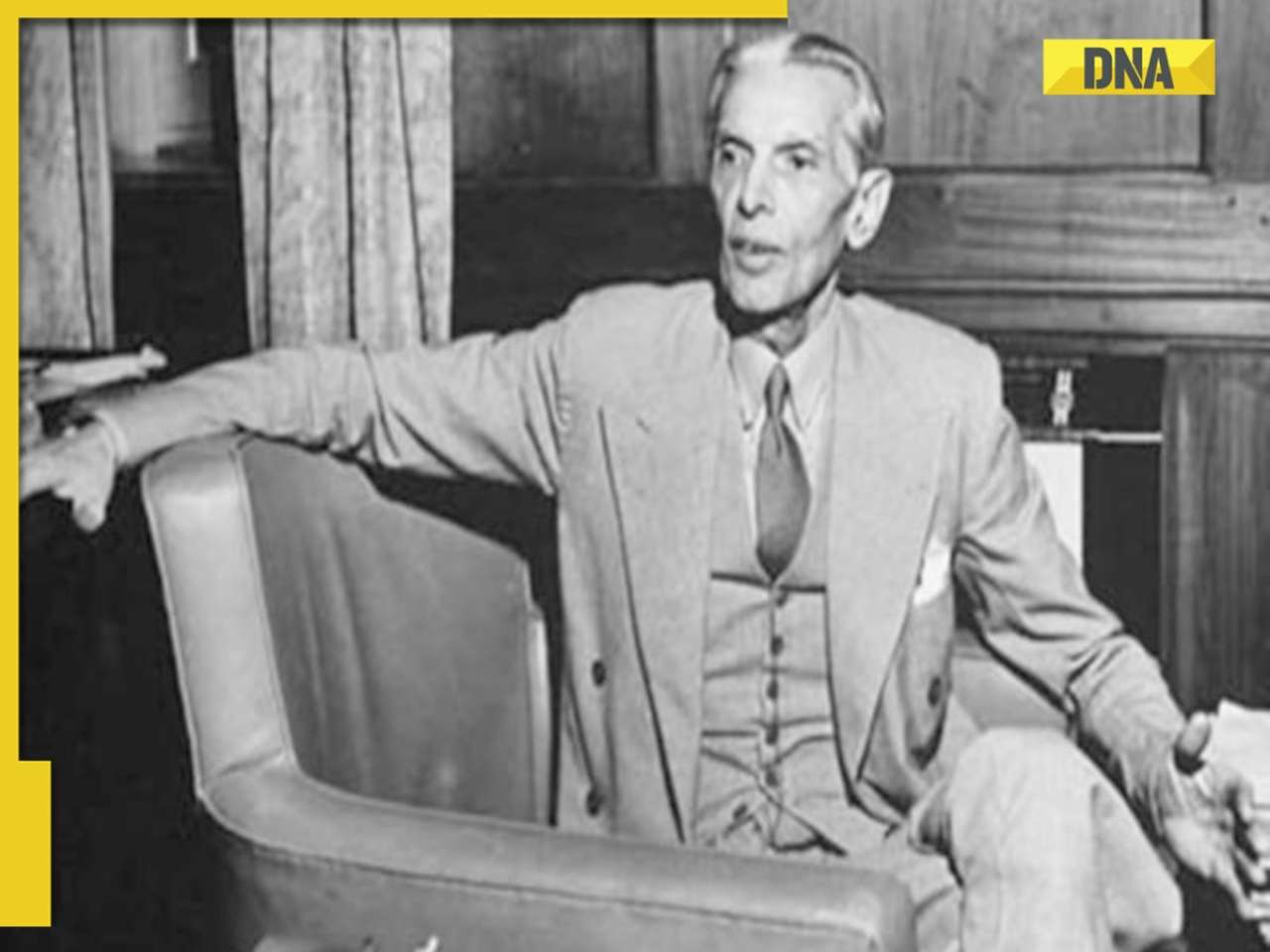

Meet man, founder of app under govt lens, also owns Rs 1000000000 business, he is..., his educational qualification is... Jinnah wanted THIS Muslim man to be first Finance Minister of Pakistan, he refused, his son is on Forbes list of billionaires

Jinnah wanted THIS Muslim man to be first Finance Minister of Pakistan, he refused, his son is on Forbes list of billionaires After India-UK FTA, New Delhi to begin talks with THIS country, because...

After India-UK FTA, New Delhi to begin talks with THIS country, because... Raksha Bandhan 2025: 5 Bollywood films to binge watch with your siblings

Raksha Bandhan 2025: 5 Bollywood films to binge watch with your siblings Remember Taarak Mehta Ka Ooltah Chashmah's Gogi aka Samay Shah? See how he looks now

Remember Taarak Mehta Ka Ooltah Chashmah's Gogi aka Samay Shah? See how he looks now Ashish Chanchlani looks dashing as he drops latest photos from Italy, fans say 'Tom Cruise fail hai aapke saamne'

Ashish Chanchlani looks dashing as he drops latest photos from Italy, fans say 'Tom Cruise fail hai aapke saamne' Are these five vintage car museums in India a must-visit for every automobile lover?

Are these five vintage car museums in India a must-visit for every automobile lover? Riddhima Kapoor Sahni looks dreamy in pastel gold embroidered ensemble as she walks for Suneet Varma at IWC 2025; SEE PICS

Riddhima Kapoor Sahni looks dreamy in pastel gold embroidered ensemble as she walks for Suneet Varma at IWC 2025; SEE PICS Good news for Railway passengers! Indian Railways rolls out new ticket booking rules for...

Good news for Railway passengers! Indian Railways rolls out new ticket booking rules for... BIG Update on Noida's Jewar International Airport Expansion: 4600 families, 7 schools affected as government to acquire...

BIG Update on Noida's Jewar International Airport Expansion: 4600 families, 7 schools affected as government to acquire... Kargil War Diwas: What is Operation Safed Sagar? When India dominated Pakistan with its air power during Kargil War on May 26

Kargil War Diwas: What is Operation Safed Sagar? When India dominated Pakistan with its air power during Kargil War on May 26 Big Boost for Ghaziabad: DMRC plans 4 metro corridors, Gokulpuri-Hindon Airport link proposed

Big Boost for Ghaziabad: DMRC plans 4 metro corridors, Gokulpuri-Hindon Airport link proposed Maharashtra monsoon: IMD issues red alert in six districts, traffic chaos in Mumbai amid heavy rain; school, colleges shut in...

Maharashtra monsoon: IMD issues red alert in six districts, traffic chaos in Mumbai amid heavy rain; school, colleges shut in... Meet woman, who studied MBBS, later cracked UPSC with AIR..., became popular IAS officer for these reasons, shares similarities with IAS Tina Dabi, she is from...

Meet woman, who studied MBBS, later cracked UPSC with AIR..., became popular IAS officer for these reasons, shares similarities with IAS Tina Dabi, she is from... Meet Nilufa Yasmine, who topped UGC NET June exam, failed twice before scoring a perfect 100, she is from...

Meet Nilufa Yasmine, who topped UGC NET June exam, failed twice before scoring a perfect 100, she is from... Meet woman, daughter of vegetable vendor who cracked UPSC, her mother mortgaged gold for her education, her AIR is…

Meet woman, daughter of vegetable vendor who cracked UPSC, her mother mortgaged gold for her education, her AIR is… Meet woman, who cracked IIT with full-time job, secured impressive AIR of...; now works at Bill Gates' Microsoft as...

Meet woman, who cracked IIT with full-time job, secured impressive AIR of...; now works at Bill Gates' Microsoft as... Meet woman, couldn't speak English, once worked at Ratan Tata's TCS, cleared ISRO, BARC exams; later cracked UPSC with AIR..., she is...

Meet woman, couldn't speak English, once worked at Ratan Tata's TCS, cleared ISRO, BARC exams; later cracked UPSC with AIR..., she is... Maruti Suzuki's e Vitara set to debut electric market at Rs..., with range of over 500 km, to launch on...

Maruti Suzuki's e Vitara set to debut electric market at Rs..., with range of over 500 km, to launch on... This is world’s most expensive wood, cost of 1kg wood is more than gold, its name is..., is found in...

This is world’s most expensive wood, cost of 1kg wood is more than gold, its name is..., is found in... This luxury car is first choice of Indians, even left BMW, Jaguar, Audi behind in sales, it is...

This luxury car is first choice of Indians, even left BMW, Jaguar, Audi behind in sales, it is... Kia India unveils Carens Clavis: Check features, design changes, price and more; bookings open on...

Kia India unveils Carens Clavis: Check features, design changes, price and more; bookings open on... Tesla CEO Elon Musk launches most affordable Cybertruck, but it costs Rs 830000 more than older version, it is worth Rs...

Tesla CEO Elon Musk launches most affordable Cybertruck, but it costs Rs 830000 more than older version, it is worth Rs...

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)